# **ACCESSING MEMORY**

Dr. Russ Meier

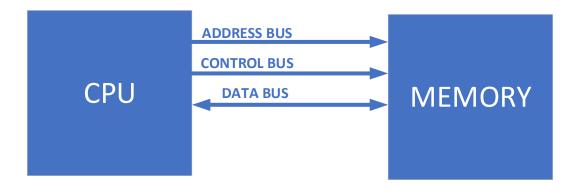

#### **MEMORY BUSSES**

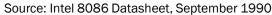

- The CPU creates three numerical memory busses

- An address bus requests access to memory locations

- A data bus is used to move data between the CPU and the memory

- A control bus contains signals controlling the memory chips

#### **MEMORY BUSSES**

- Control signals coordinate data movement using a bus protocol

- Declare address validity so memories know the address bus contains a correct number

- Declare direction of transfer using a read/write or a memory load signal

- Control speed of data flow using clock signals or other flow control signals

|          | 2  |                  |     | MAX<br>MODE  |         |

|----------|----|------------------|-----|--------------|---------|

|          |    | 0                | 40  |              | (MODE ) |

| AD14     | 2  |                  | 39  |              |         |

| AD13     | 3  |                  | 38  | EA16/S3      |         |

| AD12     | 4  |                  | 37  |              |         |

| AD11     | 5  |                  | 36  | E            |         |

| AD10     | 6  |                  | 35  | <b>—</b> ,   |         |

| AD9      | 7  |                  | 34  |              |         |

| AD8      | 8  |                  | 33  |              |         |

| AD7      | 9  |                  | 32  |              |         |

| 1000     | 10 | 8086<br>CPU      | 31  | 11 1 2 2 3 S | (HOLD)  |

| AD5      | 11 |                  | 30  |              | (HLDA)  |

| AD4      | 12 |                  | 29  |              | (WR)    |

| AD3      | 13 |                  | 28  |              | (M/IO)  |

| 10000000 | 14 |                  | 252 | Esi          | (DT/R)  |

| AD1      | 15 |                  | 26  | Eso          | (DEN)   |

| ADO      | 16 |                  | 25  | Goso         | (ALE)   |

|          | 17 |                  | 24  | Bost         | (INTA)  |

|          | 18 |                  | 23  | TEST         |         |

|          | 19 |                  | 22  | READY        |         |

|          | 20 |                  | 21  | RESET        |         |

|          |    | 40.1.4           |     | 2314         | 55-2    |

|          |    | 40 Le            | ad  |              |         |

| Fi       | -  | re 2. 8<br>nfigu |     |              |         |

|          |    |                  |     |              |         |

| S2       | S <sub>1</sub> | S <sub>0</sub> | Characteristics        |  |  |

|----------|----------------|----------------|------------------------|--|--|

| 0 (LOW)  | 0              | 0              | Interrupt Acknowledge  |  |  |

| 0        | 0              | 1              | Read I/O               |  |  |

| 0        | 1              | 0              | Write I/O              |  |  |

| 0        | 1              | 1              | Halt                   |  |  |

| 1 (HIGH) | 0              | 0              | Instruction Fetch      |  |  |

| 1        | 0              | 1              | Read Data from Memory  |  |  |

| 1        | 1              | 0              | Write Data to Memory   |  |  |

| 1        | 1              | 1              | Passive (no bus cycle) |  |  |

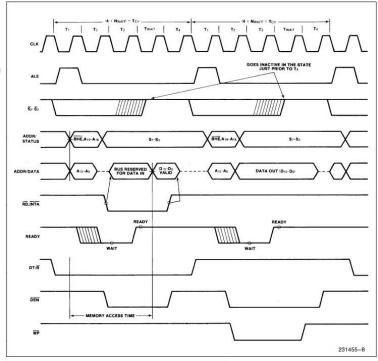

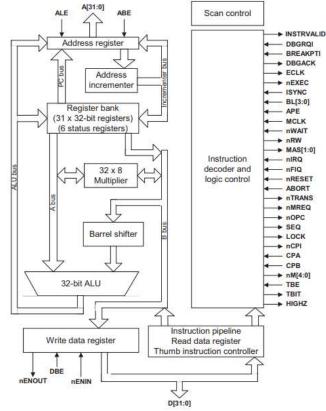

Source: ARM7TDMI Technical Reference Manual, 2004

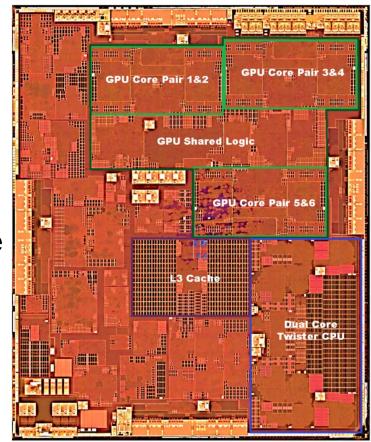

# CACHE MEMORY

- Fabricated on CPU silicon die

- Multiple levels of cache exist

- This image is the Apple A9

- Dual-core ARMv8 CPU

- Level 1 and Level 2 in CPU Core

- L3 on-chip

- Accessed by the memory bus

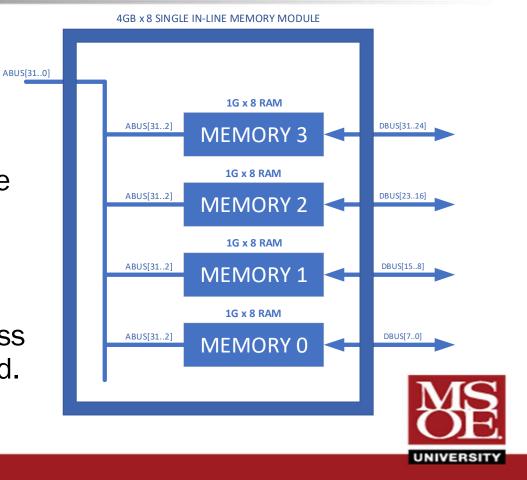

#### **MAIN MEMORY**

- This example shows a full 32-bit 4GB address space using four 1GB memories.

- Each memory provides its byte at the specified address.

- Since four-bytes are provided, the memory is 32-bit aligned.

- Note that the upper 30 address bits specified the desired word.

#### MAIN MEMORY

- This example shows a DDR2 256MiB single in-line memory module (SIMM) for a personal computer.

- DDR2 uses a 64-bit data bus.

- Each chip is 32MiB of storage.

- Each chip provides its byte in the 64-bit word.

- 32MiB x 8 = 256MiB

R2

R3

R4

0x80000000

- ARM accesses memory as a large array of 32-bit numbers.

- Consider the Java code:

j = A[0]

The load-register instruction implements this equation as:

$R[Rd] \leftarrow MEM[Rn,#0]$

An array of five integers stored in memory

| 5.               |            | ADDRESS    | DATA WORD  |            |  |  |

|------------------|------------|------------|------------|------------|--|--|

| MO               | V R4,#0x80 | 000000     | 0x80000000 | 0xAB94C600 |  |  |

| LDR R0, [R4, #0] |            | 0x80000004 | 0xBADCAB02 |            |  |  |

| REGISTER V       |            | VALUE      | 0x8000008  | 0x01234567 |  |  |

|                  | RO         | 0xAB94C600 | 0x8000000C | 0x000FF99B |  |  |

|                  | R1         |            | 0x80000010 | 0xFEDCBA98 |  |  |

R4 is a memory address R4 is a "pointer" into memory R4 is a "reference" to the memory location

- ARM allows an index of 0 to be omitted in assembly language.

- Consider the Java code:

j = A[0]

The load-register instruction implements this equation as:

$R[Rd] \leftarrow MEM[Rn]$

| 1.10 | V I(I, TOXOC |            | UX  |

|------|--------------|------------|-----|

| LDI  | R R0,[R4]    |            | Ox  |

|      | REGISTER     | VALUE      | 0x  |

|      | RO           | 0xAB94C600 | Ox  |

|      | R1           |            | 0x  |

| :    | R2           |            |     |

|      | R3           |            | R4  |

|      | R4           | 0x8000000  | 117 |

An array of five integers stored in memory

| <u>с.</u> |            | ADDRESS    | DATA WORD  |            |

|-----------|------------|------------|------------|------------|

| MO        | V R4,#0x80 | 000000     | 0x80000000 | 0xAB94C600 |

| LDI       | R R0,[R4]  |            | 0x80000004 | 0xBADCAB02 |

| REGISTER  |            | VALUE      | 0x8000008  | 0x01234567 |

|           | RO         | 0xAB94C600 | 0x8000000C | 0x000FF99B |

|           | R1         |            | 0x80000010 | 0xFEDCBA98 |

R4 is a memory address R4 is a "pointer" into memory 4 is a "reference" to the memory location

R2

R3

R4

0x80000000

• Consider the Java code:

An array of five integers stored in memory

j = A[3]

The load-register instruction implements this equation as:

$R[Rd] \leftarrow MEM[Rn,#12]$

|                    |    | ADDRESS    | DATA WORD  |            |  |  |

|--------------------|----|------------|------------|------------|--|--|

| MOV R4,#0x80000000 |    | 0x80000000 | 0xAB94C600 |            |  |  |

| LDR R0, [R4, #12]  |    | 0x80000004 | 0xBADCAB02 |            |  |  |

| REGISTER VALUE     |    | VALUE      | 0x8000008  | 0x01234567 |  |  |

| ).                 | RO | 0x000FF99B | 0x8000000C | 0x000FF99B |  |  |

|                    | R1 |            | 0x80000010 | 0xFEDCBA98 |  |  |

R4 is a memory address R4 is a "pointer" into memory R4 is a "reference" to the memory location

MOV R4, #0x80000000 ----

LDR R0, [R4, #12]

- In this example, R4 is the pointer.

- R4 can also be called the base address.

- The displacement is 12.

- The final memory address is calculated as base address + displacement. The final memory address is called the effective memory address.

An array of five integers stored in memory

| ADDRESS    | DATA WORD  |

|------------|------------|

| 0x8000000  | 0xAB94C600 |

| 0x80000004 | 0xBADCAB02 |

| 0x8000008  | 0x01234567 |

| 0x8000000C | 0x000FF99B |

| 0x80000010 | 0xFEDCBA98 |

R4 is a memory address R4 is a "pointer" into memory R4 is a "reference" to the memory location

#### ADDRESSING MODE

• We have now seen three addressing modes in class.

| ADDRESSING MODE        | EXAMPLE         | ADDRESS IN MEMORY | PSEUDO-CODE  |

|------------------------|-----------------|-------------------|--------------|

| Literal                | MOV R4,#10      | None needed       | INT J = 10   |

| Base                   | LDR R4,[R2]     | R2 + 0            | INT J = A[O] |

| Base with displacement | LDR R4,[R2,#16] | R2 + 16           | INT J = A[4] |

Base with displacement is also called base with offset

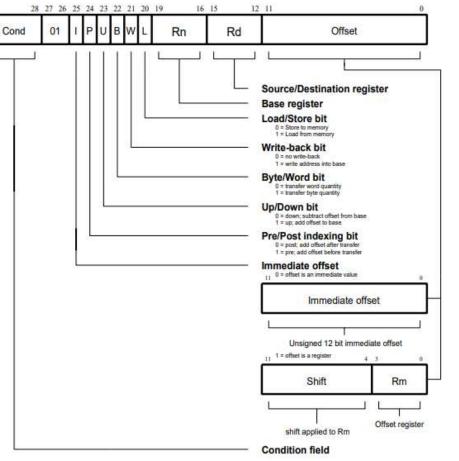

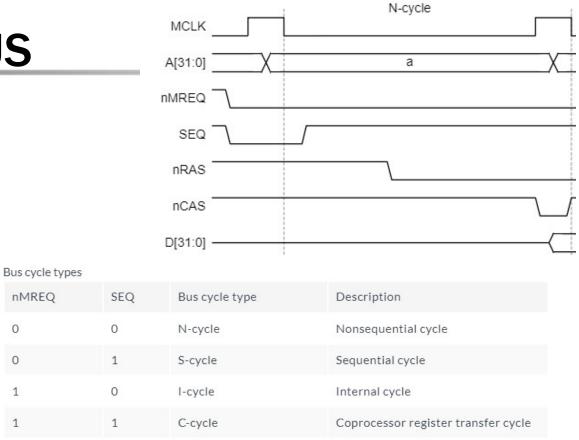

# **ENCODING LDR AND STR INSTRUCTIONS**

| EXAMPLE          | ADDRESSING MODE | INDEX MODE         | MEMORY ADDRESS | OP | Ī | Ρ | U | В | W | L |

|------------------|-----------------|--------------------|----------------|----|---|---|---|---|---|---|

| LDR R4,[R5,R6]   | BASE + OFFSET   | PRE-INDEX ADD R6   | R5 + R6        | 01 | 1 | 1 | 1 | 0 | 0 | 1 |

| LDR R4,[R5]      | BASE + OFFSET   | PRE-INDEX ADD #0   | R5             | 01 | 0 | 1 | 1 | 0 | 0 | 1 |

| LDR R4,[R5,#12]  | BASE + OFFSET   | PRE-INDEX ADD #12  | R5 + 12        | 01 | 0 | 1 | 1 | 0 | 0 | 1 |

| STR R4,[R5,#-20] | BASE + OFFSET   | PRE-INDEX ADD #-20 | R5 – 20        | 01 | 0 | 1 | 0 | 0 | 0 | 0 |

#### These are the only types of LDR and STR used in CE1921

UNIVERSITY

#### **ENCODING LDR AND STR INSTRUCTIONS**

#### ARM Data Sheet Image Showing Encoding Format